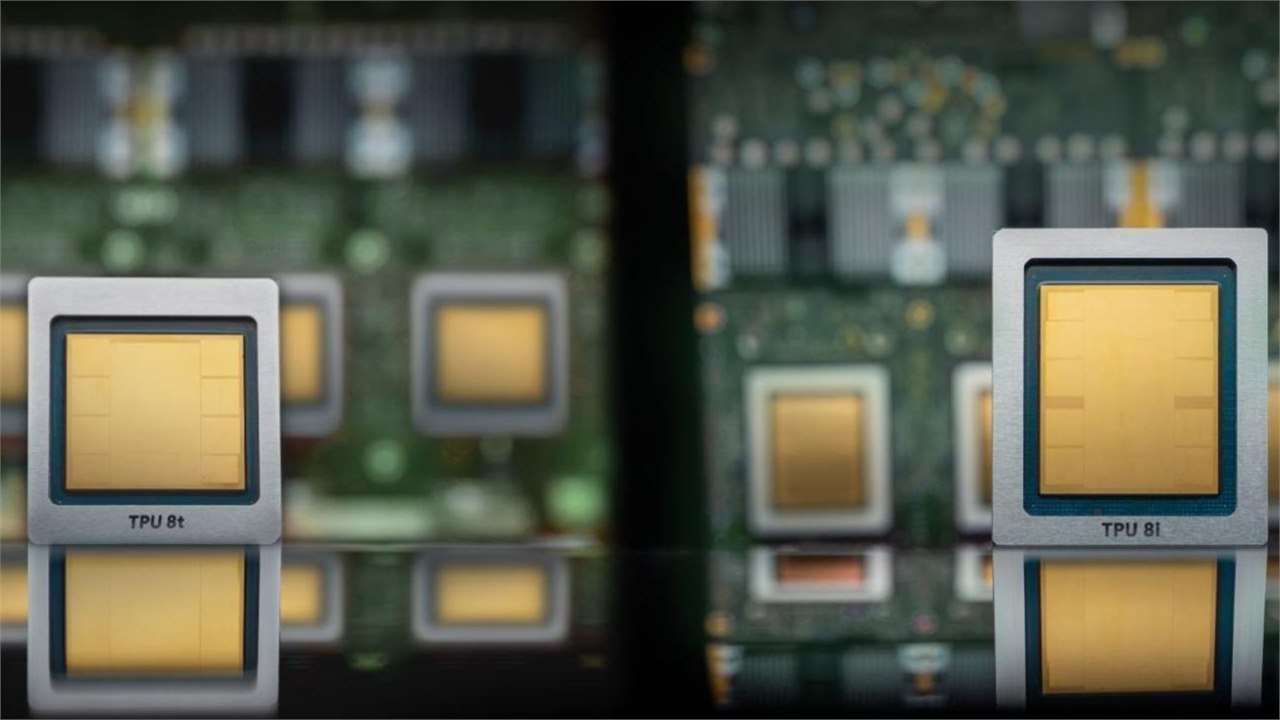

Google công bố TPU V8 với hai chip 8t và 8i, mỗi loại được thiết kế cho các tác vụ AI cụ thể, nhằm tăng cường khả năng xử lý và mở rộng quy mô trên nền tảng đám mây.

Äá»c tiếp

Vá» Góc nhìn

Mở hub G�c nh�n để xem thêm các bài cùng mạch nội dung.

Xem thêm AI

Khám phá thêm các bài cùng chuyên mục ai.

OpenAI phát triển smartphone AI: Tác nhân thông minh thay thế ứng dụng truyền thống

AI • 09:01 28/04/2026

Bài viết AI vượt 50% trên web: Tốc độ tăng trưởng chóng mặt

AI • 09:01 28/04/2026

Äiểm chÃnh

- Google ra mắt TPU V8 với hai chip 8t (đào tạo quy mô lớn) và 8i (suy luận độ trễ thấp), đánh dấu lần đầu tiên có hai thiết kế chuyên biệt.

- Chiến lược tập trung vào khả năng mở rộng quy mô siêu lớn (lên đến 1 triệu chip) và tối ưu chi phí, thay vì cạnh tranh hiệu năng đơn chip với Nvidia.

- TPU 8i sử dụng kiến trúc Boardfly mới thay thế 3D Torus, giúp giảm độ trễ giao tiếp và cải thiện hiệu quả cho mô hình Mixture-of-Experts (MoE).

- Cả hai chip đều sử dụng CPU Arm Axion và được sản xuất bởi nhiều nhà cung cấp (MediaTek, Broadcom), góp phần giảm chi phí sản xuất.

Google TPU V8 và Chiến Lược Hai Chip Độc Đáo

Tại sự kiện Cloud Next gần đây, Google đã chính thức công bố thế hệ chip xử lý Tensor (TPU) thứ 8 của mình, đánh dấu một bước tiến quan trọng trong lĩnh vực trí tuệ nhân tạo. Đây là lần đầu tiên trong lịch sử 10 năm của chương trình TPU, Google giới thiệu hai thiết kế chip riêng biệt: TPU 8t và TPU 8i.

TPU 8t được tối ưu hóa cho các tác vụ đào tạo mô hình AI quy mô lớn, đòi hỏi khả năng xử lý dữ liệu khổng lồ. Trong khi đó, TPU 8i được thiết kế đặc biệt để phục vụ các khối lượng công việc suy luận (inference) với độ trễ thấp, nơi tốc độ phản hồi là yếu tố then chốt.

Cả hai chip này đều được sản xuất trên tiến trình N3 tiên tiến của TSMC và sử dụng bộ nhớ HBM3E hiệu suất cao. Chúng dự kiến sẽ sớm có mặt cho các khách hàng của Google Cloud vào cuối năm nay.

Khả Năng Mở Rộng Quy Mô Khổng Lồ và Tối Ưu Chi Phí

Mặc dù về mặt thông số kỹ thuật thô, TPU V8 có thể chưa thu hẹp được khoảng cách hiệu suất đơn chip so với các đối thủ như Nvidia hay AMD, chiến lược của Google lại tập trung vào khả năng mở rộng quy mô ở cấp độ hệ thống. TPU 8t có thể được triển khai trong các siêu pod lên tới 9.600 chip, cung cấp 121 FP4 ExaFLOPs.

Điểm mạnh vượt trội của Google nằm ở khả năng kết nối hàng triệu TPU trong một cụm thông qua mạng Virgo Network độc quyền, mang lại băng thông bisection lên tới 47 PB/s. Điều này tạo ra một lợi thế đáng kể cho các tác vụ đào tạo AI khổng lồ cần hàng nghìn bộ tăng tốc hoạt động đồng thời, nơi các GPU hiện tại của Nvi...

Việc lựa chọn bộ nhớ HBM3E thay vì HBM4 cho thấy Google đang ưu tiên tối ưu chi phí và sản lượng. Dù băng thông có phần thấp hơn thế hệ trước, chiến lược này giúp Google cung cấp các lựa chọn thay thế cạnh tranh về giá thành cho khách hàng muốn đa dạng hóa hạ tầng AI của mình.

Kiến Trúc Mới của TPU 8i và Lợi Ích Thực Tế

TPU 8i mang đến một sự thay đổi kiến trúc đáng kể khi loại bỏ kết nối 3D Torus truyền thống, thay vào đó là cấu trúc liên kết Boardfly mới. Lấy cảm hứng từ nghiên cứu Dragonfly năm 2008, Boardfly giảm đáng kể số bước nhảy gói tin trong mạng (từ 16 xuống 7 trong cấu hình 1.024 chip).

Sự cải tiến này đặc biệt có lợi cho các mô hình Mixture-of-Experts (MoE), nơi yêu cầu giao tiếp toàn bộ (all-to-all) thường xuyên giữa các cặp chip không thể đoán trước. Việc giảm độ trễ mạng trực tiếp cải thiện hiệu suất của các mô hình này.

Ngoài ra, TPU 8i còn thay thế SparseCore bằng Collectives Acceleration Engine (CAE) mới, giúp giảm độ trễ của các hoạt động giảm và đồng bộ hóa lên đến năm lần. Kết hợp với SRAM được tăng gấp ba, TPU 8i mang lại hiệu suất trên mỗi đô la tốt hơn 80% so với thế hệ trước cho các mô hình MoE lớn ở mức độ trễ thấp.

Đáng chú ý, cả TPU 8t và 8i đều lần đầu tiên chạy trên các máy chủ CPU Arm-based Axion của Google, thay thế kiến trúc x86 truyền thống.

Đa Dạng Chuỗi Cung Ứng và Hút Khách Hàng Lớn

Để tối ưu hóa chuỗi cung ứng và giảm chi phí, Google đã hợp tác với MediaTek để thiết kế chip 8i, trong khi Broadcom tiếp tục phụ trách thiết kế chip 8t. Sự đa dạng hóa này có thể giúp giảm chi phí mỗi chip lên tới 30% so với việc chỉ dựa vào một nhà cung cấp.

Các đối tác lớn đã thể hiện sự quan tâm đáng kể đến hạ tầng TPU của Google. Anthropic đã cam kết sử dụng công suất TPU tương đương 3.5 gigawatt từ năm 2027. Meta cũng ký thỏa thuận thuê TPU trị giá hàng tỷ đô la, dự kiến sử dụng 500.000 đến 800.000 chip TPU vào năm 2027. Apple cũng đang chuyển các khối lượng công vi...

Điều thú vị là Google cũng công bố các phiên bản Nvidia Vera Rubin NVL72 chạy trên cùng mạng Virgo Network, cho thấy Google không chỉ muốn thay thế mà còn bổ sung các giải pháp AI đa dạng cho khách hàng của mình.

Nguồn gốc

Bà i viết được biên táºp lại bằng tiếng Việt từ nguồn gốc, Æ°u tiên rõ ý, ngắn Ä‘oạn và giữ link đối chiếu.

FAQ

- TPU V8 của Google có gì đặc biệt? Đây là thế hệ TPU đầu tiên có hai chip chuyên biệt: 8t cho đào tạo AI quy mô lớn và 8i cho suy luận AI độ trễ thấp, tập trung vào khả năng mở rộng hệ thống và tối ưu chi phí.

- Google TPU V8 có cạnh tranh trực tiếp với chip AI của Nvidia không? Về hiệu năng đơn chip, TPU V8 không vượt trội. Tuy nhiên, Google tập trung vào khả năng mở rộng quy mô siêu lớn (hàng triệu chip trong một cụm) và tối ưu chi phí, mang lại lợi thế ở cấp độ pod cho các tác vụ AI khổng lồ.

- Lợi ích của kiến trúc Boardfly trên TPU 8i là gì? Kiến trúc Boardfly mới trên TPU 8i giúp giảm đáng kể số bước nhảy mạng, từ đó giảm độ trễ giao tiếp và cải thiện hiệu quả cho các mô hình AI phức tạp như Mixture-of-Experts, vốn đòi hỏi giao tiếp liên tục giữa các chip.